Übersicht über die Vorlesungen

Weitere Informationen zu dem Lehrveranstaltungsangebot von INES finden Sie auch im C@MPUS System der Universität Stuttgart

Sommersemester

Voraussetzungen

Basic knowledge of micro/nanoelectronic devices is recommened

- gain understanding of the integration concepts of microelectronic devices and interconnects in CMOS,

- understand the physics and electrical characteristics of ideal CMOS devices,

- can identify the device non-idealities that result from constraints in process technology,

- know about non-ideal effects in deep-submicrometer CMOS transistors,

- understand CMOS miniaturization (scaling)

- receive an insight in the concepts of CMOS compact transistor modeling,

- understand the CMOS inverter circuit

- get an overview of volume manufacturing concepts, including yield and cost estimation

Comprehensive illustration of CMOS technology:

- History and Basics of IC Technology

- Process Technology I and II

- Process Modules

- MOS Capacitor

- Non-Ideal MOS Transistor

- Basics of CMOS Circuit Integration

- CMOS Device Scaling

- Metal-Silicon Contact

- Interconnects

- Design Metrics

- Special MOS Devices

- Future Directions

Anmerkung

Die Vorlesung "Fundamentals of Microelectronics" ist identisch mit der Vorlesung "Advanced CMOS Devices and Technology" und wird zeitgleich abgehalten. Lediglich die Zuordnung erfolgt zu einem anderen Modul.

Voraussetzungen

Basic knowledge of micro/nanoelectronic devices is recommened

- gain understanding of the integration concepts of microelectronic devices and interconnects in CMOS,

- understand the physics and electrical characteristics of ideal CMOS devices,

- can identify the device non-idealities that result from constraints in process technology,

- know about non-ideal effects in deep-submicrometer CMOS transistors,

- understand CMOS miniaturization (scaling)

- receive an insight in the concepts of CMOS compact transistor modeling,

- understand the CMOS inverter circuit

- get an overview of volume manufacturing concepts, including yield and cost estimation

Comprehensive illustration of CMOS technology:

- History and Basics of IC Technology

- Process Technology I and II

- Process Modules

- MOS Capacitor

- Non-Ideal MOS Transistor

- Basics of CMOS Circuit Integration

- CMOS Device Scaling

- Metal-Silicon Contact

- Interconnects

- Design Metrics

- Special MOS Devices

- Future Directions

Weitere Informationen zu dem Lehrveranstaltungsangebot von INES finden Sie auch im C@MPUS System der Universität Stuttgart

Versuchsbeschreibung / -durchführung am Institut für Mikroelektronik Stuttgart im Sommersemester 2024

Die Versuche

1. Simulation eines CMOS-Bauelements mit Silvaco®-Tools

2. Entwicklung und Entwurf integrierter Schaltungen

3. Chip-Packaging – AVT-Versuch

4. Optische Temperatur-Sensorik – Thermopile-Kalibrierkurve

Beschreibung

- Vom Halbeitermaterial bis zum CMOS Bauelement.

Am Beispiel eines CMOS-Transistors sollen die Teilnehmer/innen mithilfe des Simulations-Tools Silvaco ein Verständnis über die Auswirkungen von Parametervariationen (geometrisch, Dotierung, ...) auf die grundlegenden Eigenschaften bzw. das Verhalten eines Halbleiter- Bauelementes erlangen.

(max. 12 Teilnehmer, Dauer ca. 3 V-St.). - Von der Idee bis zum Kunden spezifischen integrierten Schaltkreis (ASIC).

Im Rahmen dieses Praktikumsversuchs sollen die Teilnehmer/innen einen kompakten Überblick über die wichtigsten Schritte (Spezifikation, Schaltungs-Entwurf, Fehlerprüfungen, Fertigung) bei der Entwicklung und Herstellung von integrierten Schaltungen anhand eines Inverters erhalten.

(max. 12 Teilnehmer, Dauer ca. 3 V-St.). - Vom Wafer bis zum fertigen elektronischen Bauteil.

Der Praktikumsblock befasst sich mit den wichtigsten Schritten beim Aufbau und Verpacken (Wafer rückdünnen und sägen, einkleben und Bonden der einzelnen Chips, verschließen und Kennzeichnung der Gehäuse) von Halbleiter Chips. Am praktischen Beispiel des Bond-Prozesses wird den Teilnehmer/innen die einzelnen Schritte beim Chip Bonden verdeutlicht.

(max. 8 Teilnehmer, Dauer ca. 2-3 V-St.). - Vom elektronischen Bauteil bis zum Einsatz.

In der berührungslosen Temperaturmesstechnik können die einzelnen Sensorbauelemente

z.B. Thermopiles nicht direkt eingesetzt werden, sie müssen zuvor aufwendig kalibriert werden. Die Teilnehmer/innen werden hierbei die Kalibrierkennlinie eines Standard-Thermopiles an einem Infrarot-Messplatz vermessen / dokumentieren und ein grundlegendes Verständnis über die Einflüsse am Beispiel eines Temperatursensors auf das Messergebnis erlangen.

(max. 8 Teilnehmer, Dauer ca. 3 V-St.).

Gesamtzahl der Teilnehmer

Versuch 1 + 2: 1 Gruppe ➔ 2 – 12 Teilnehmer/innen

Versuch 3 + 4: 2 Gruppen ➔ 2 – 4 Teilnehmer/innen / Gruppe

1V-St. ⇒ 45 min.

Ort

IInstitut für Mikroelektronik Stuttgart - IMS CHIPS, Allmandring 30a, 70569 Stuttgart

Beginn: jeweils um 14:00 Uhr

Versuche 1 – 2: Schulungsraum PC

Versuch 3: Chipmontage

Versuch 4: Opto-Messplatz

Die Termine für das Sommersemester 2024

Anmeldestart: 01.03.2024

Anmeldeschluss: 31.05.2024

Allgemeines Praktikum Maschinenbau am IMS CHIPS im Sommersemester 2024 (PDF)

Wintersemester

Blockseminar für das Wintersemester 23 / 24

Zeit: 11. - 13. Oktober 2023 jeweils 9 - 17 Uhr

Ort: IMS CHIPS, Allmandring 30A, 70569 Stuttgart-Vaihingen

Agenda

Mittwoch 11.10. 2023

09:00 1. Mikroelektronik verändert die Welt

Spitzentechnologie im ständigen Wandel

10:15 2. Vom elektronischen System zur Siliziumstruktur I

11:30 2. Vom elektronischen System zur Siliziumstruktur II

12:30 Mittagspause

13:30 3. Lithographie I

15:15 3. Lithographie II

17:00 A. Hausarbeiten + Prüfungsablauf f. Studenten der Uni Stuttgart

Donnerstag 12.10. 2023

09:00 4. Wafer-Prozesse I: Scheibenherstellung & thermische Prozesse

10:45 4. Wafer-Prozesse II: Schichtabscheidung

12:30 Mittagspause

13:30 4. Wafer-Prozesse III: Dotierung

15:15 4. Wafer-Prozesse IV: Ätzung

17:00 B1. Technologieführung

Freitag 13.10. 2023

09:00 5. CMOS-Gesamtprozesse I

10:15 5. CMOS-Gesamtprozesse II

11:30 6. Aufbau- und Verbindungstechnik (AVT)

12:30 Mittagspause

13:30 7. Test mikroelektronischer Schaltungen

14:45 8. Qualität und Zuverlässigkeit

16:00 B2. Technologieführung

Bitte beachten:

Direkte Anmeldung mit Studiengang / Abschluss und Matrikel Nr. ist erforderlich!

Vergabe der begrenzten Teilnehmerplätze erfolgt nach zeitlichem Eingang der Anmeldungen:

Anmeldung bei E. Futterer +49 711 21855-260 per Email an: efu@ims-chips.de

Lernziele

Die Studierenden erlangen grundlegende Kenntnisse über Aufbau und Wirkungsweise von integrierten Mikrosystemen.

Inhalt

- Grundlegende Kenntnisse der Funktionsweise von MOS-Transistoren und deren Entwurf am Computer.

- Übersicht über wichtige funktionale Grundschaltungen integrierter Schaltungen (Stromspiegel, Bandgap-Schaltungen, Operationsverstärker, Komparatoren).

- Funktionsweise von integrierbaren Sensoren aus den Bereichen Optik, Magnetik und Mechanik.

- Entwurf von integrierten Schaltungen (Grundlagen zum Layout).

Beginn

- Di, 18.10.2022

Lernziele

Die Studierenden erlangen grundlegende praktische Kenntnisse über die Simulation und das Layout von integrierten Schaltungen und Photosensoren.

Inhalt

Das Praktikum vertieft das Verständnis des Transistors durch Simulation von verschiedenen Schaltungen. Ausgehend von Transistorkennlinien und daraus abgeleiteten Größen werden einfache Schaltungen mit LTspice entworfen und simuliert.

Im zweiten Teil des Praktikums werden einfache Grundschaltungen wie Inverter, NAND-Gatter, Ringsoszillatoren und Bildsensorzellen entworfen. Mit Hilfe einer Designumgebung (Cadence oder KLayout) werden die Schaltungen in ein Layout umgesetzt.

Anmerkung

Die praktische Arbeit ist nur in Kombination mit der Vorlesung möglich.

Termine

- 24.11.2022

- 01.12.2022

- 08.12.2022

- 12.01.2023

- 19.01.2023

- 26.01.2023

Blockseminar für das Wintersemester 22 / 23

12. - 14. Oktober 2022 jeweils 9:00 – ca. 17:00 Uhr

Seminarraum (AR30A/U1/U1.193) im C@MPUS System

Institut für Mikroelektronik Stuttgart (IMS CHIPS)

Allmandring 30A, 70569 Stuttgart

Agenda

Mittwoch 12.10. 2022

09:00 1. Mikroelektronik verändert die Welt

Spitzentechnologie im ständigen Wandel

10:15 2. Vom elektronischen System zur Siliziumstruktur I

11:30 2. Vom elektronischen System zur Siliziumstruktur II

12:45 Mittagspause

13:45 3. Lithographie I

15:15 3. Lithographie II

17:00 A. Hausarbeiten + Prüfungsablauf f. Studenten der Uni Stuttgart

Donnerstag 13.10. 2022

09:00 4. Wafer-Prozesse I: Scheibenherstellung & thermische Prozesse

10:45 4. Wafer-Prozesse II: Schichtabscheidung

12:45 Mittagspause

13:45 4. Wafer-Prozesse III: Dotierung

15:30 4. Wafer-Prozesse IV: Ätzung

17:00 B1. Technologieführung

Freitag 14.10. 2022

09:00 5. CMOS-Gesamtprozesse I

10:45 5. CMOS-Gesamtprozesse II

11:30 6. Aufbau- und Verbindungstechnik (AVT)

12:45 Mittagspause

13:45 7. Test mikroelektronischer Schaltungen

14:45 8. Qualität und Zuverlässigkeit

15:45 B2. Technologieführung

Bitte beachten:

Direkte Anmeldung mit Studiengang / Abschluss und Matrikel Nr. ist erforderlich!

Vergabe der begrenzten Teilnehmerplätze erfolgt nach zeitlichem Eingang der Anmeldungen:

Anmeldung bei E. Futterer +49 711 21855-260 per Email an: efu@ims-chips.de

Voraussetzungen

Kenntnisse im Umfang der Vorlesungen (B. Sc.): Mikroelektronik, Halbleitertechnik, Halbleitertechnologie

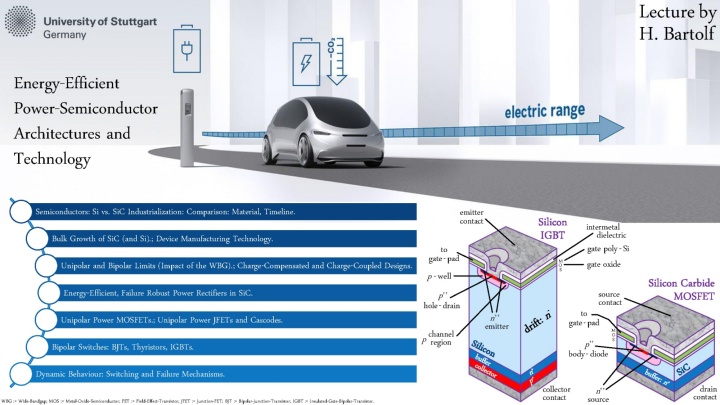

Lernziele

Die Studierenden haben ein umfassendes Verständnis des Designs von Energie-effizienten Halbleiter-Architekturen unter Miteinbeziehung von Aspekten der Prozesstechnologie um das Verständnis der kosteneffizienten Produktionsmethoden für Hochvolumina von Halbleiterchips mit hoher Qualität und Zuverlässigkeit zu fördern.

Der Fokus wird auf das Material Silizium Carbid (SiC; ein sogenannter WBG Halbleiter) und dessen Schlüsselrolle in der Elektromobilität gelegt.

Inhalt

Die Vorlesung beinhaltet die folgenden Fokusthematiken:

- Semiconductors: Si vs. SiC Industrialization: Comparison: Material, Timeline.

- Bulk Growth of SiC (and Si).

- Device Manufacturing Technology.

- Unipolare und Bipolare Limits (the impact of the WBG).

- Charge Compensated and Charge-Coupled Designs.

- Energy-Efficient, Failure Robust Power Rectifiers in SiC.

- Unipolar Power MOSFETs:

- MOS-interface physics; ultra-brief: V,D,U-MOS architectures.

- Si: SC, CC, SJ, GD-CC architectures.

- SiC: planar, AccuFET, deep p++ - plug architectures: 1, 2.

- Unipolar Power JFETs and Cascodes.

- Bipolar Switches: BJTs, Thyristors, IGBTs.

- Dynamic Behaviour: Switching and Failure Mechanisms.

Weitere Informationen zu dem Lehrveranstaltungsangebot von INES finden Sie auch im C@MPUS System der Universität Stuttgart

Weitere Informationen zu dem Lehrveranstaltungsangebot von INES finden Sie auch im C@MPUS System der Universität Stuttgart

Versuchsbeschreibung / -durchführung am Institut für Mikroelektronik Stuttgart im Wintersemester 2023/24

Die Versuche

1. Simulation eines CMOS-Bauelements mit Silvaco®-Tools

2. Entwicklung und Entwurf integrierter Schaltungen

3. Chip-Packaging – AVT-Versuch

4. Optische Temperatur-Sensorik – Thermopile-Kalibrierkurve

Beschreibung

- Vom Halbeitermaterial bis zum CMOS Bauelement.

Am Beispiel eines CMOS-Transistors sollen die Teilnehmer/innen mithilfe des Simulations-Tools Silvaco ein Verständnis über die Auswirkungen von Parametervariationen (geometrisch, Dotierung, ...) auf die grundlegenden Eigenschaften bzw. das Verhalten eines Halbleiter- Bauelementes erlangen.

(max. 12 Teilnehmer, Dauer ca. 3 V-St.). - Von der Idee bis zum Kunden spezifischen integrierten Schaltkreis (ASIC).

Im Rahmen dieses Praktikumsversuchs sollen die Teilnehmer/innen einen kompakten Überblick über die wichtigsten Schritte (Spezifikation, Schaltungs-Entwurf, Fehlerprüfungen, Fertigung) bei der Entwicklung und Herstellung von integrierten Schaltungen anhand eines Inverters erhalten.

(max. 12 Teilnehmer, Dauer ca. 3 V-St.). - Vom Wafer bis zum fertigen elektronischen Bauteil.

Der Praktikumsblock befasst sich mit den wichtigsten Schritten beim Aufbau und Verpacken (Wafer rückdünnen und sägen, einkleben und Bonden der einzelnen Chips, verschließen und Kennzeichnung der Gehäuse) von Halbleiter Chips. Am praktischen Beispiel des Bond-Prozesses wird den Teilnehmer/innen die einzelnen Schritte beim Chip Bonden verdeutlicht.

(max. 8 Teilnehmer, Dauer ca. 2-3 V-St.). - Vom elektronischen Bauteil bis zum Einsatz.

In der berührungslosen Temperaturmesstechnik können die einzelnen Sensorbauelemente

z.B. Thermopiles nicht direkt eingesetzt werden, sie müssen zuvor aufwendig kalibriert werden. Die Teilnehmer/innen werden hierbei die Kalibrierkennlinie eines Standard-Thermopiles an einem Infrarot-Messplatz vermessen / dokumentieren und ein grundlegendes Verständnis über die Einflüsse am Beispiel eines Temperatursensors auf das Messergebnis erlangen.

(max. 8 Teilnehmer, Dauer ca. 3 V-St.).

Vorträge und Versuche

Die Veranstaltungen finden in deutscher Sprache statt.

Versuchsbeschreibung / -durchführung am IMS CHPS im Wintersemester 2023/24 (PDF)

Kontakt

Ehrenfried Futterer

Studentische Beratung & Lehrveranstaltungen